Принцип работы ОЗУ

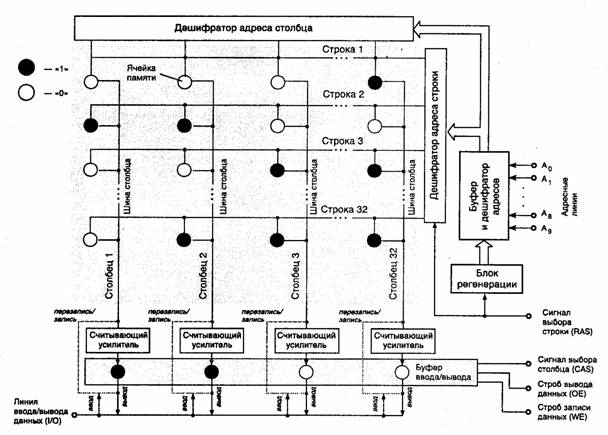

Ячейки памяти организованы в матрицу, состоящую из строк и столбцов. Полный адрес ячейки данных включает два компонента — адрес строки (row Адрес, бит) и адрес столбца (column Адрес, бит). На рис. 1 представлена матрица, состоящая из 32 строк и 32 столбцов, то есть из 1024 ячеек.

Рис. 1. Структурная схема динамической памяти

Когда CPU (или устройство, использующее канал DMA) обращается к памяти для чтения информации, на входы микросхемы поступает строб вывода данных ОЕ (Output Enabled), затем подается адрес строки и одновременно с ним (или с задержкой) сигнал RAS (Row Адрес, бит Strobe). Это означает, что каждая шина столбца соединяется с ячейкой памяти выбранной строки. Адрес ячейки поступает по адресным линиям (в нашем случае их десять) на дешифратор, который преобразует поступивший набор нулей и единиц в номер строки. Емкость конденсатора очень мала (доли пикофарады) и его заряд тоже мал, поэтому используется усилитель, подключенный к каждой шине столбца динамической памяти. Информация считывается со всей строки запоминающих элементов одновременно и помещается в буфер ввода/вывода. С незначительной задержкой после сигнала RAS на входы динамической памяти подается адрес столбца и сигнал CAS (Column Адрес, бит Strobe). При чтении данные выбираются из буфера ввода/вывода и поступают на выход динамической памяти в соответствии с адресом столбца. При считывании информации из ячеек памяти происходит ее разрушение, поэтому производится перезапись считанной информации: выходы регистра строки снова соединяются с общими шинами столбцов памяти, чтобы перезаписать считанную информацию из строки. Если ячейка имела заряд, то она снова будет заряжена еще до завершения цикла чтения. На ячейки, которые не имели заряда, напряжение не подается.

Если выполняется запись в память, то подается строб записи WE (Write Enable) и информация поступает на соответствующую шину столбца не из буфера, а с входа памяти в соответствии с адресом столбца. Таким образом, прохождение данных при записи задается комбинацией сигналов, определяющих адрес столбца и строки, а также сигналом разрешения записи данных в память.

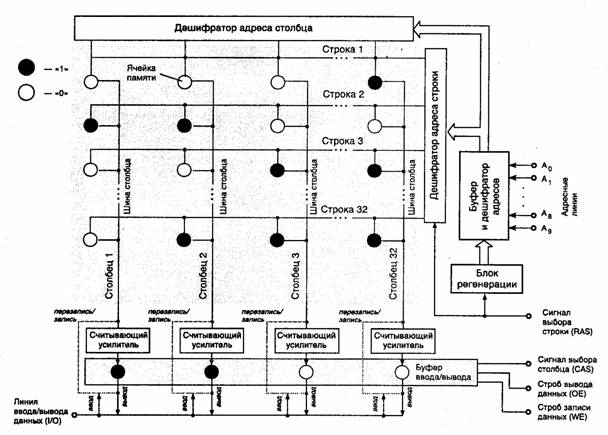

На рис. 1 представлена структура микросхемы памяти, имеющая одну линию ввода/вывода. Из такой микросхемы CPU может одновременно считать (записать) только один бит данных. Для повышения скорости обмена данными между CPU и памятью были разработаны микросхемы, имеющие 4, 8,16 и 32 линии ввода/вывода. Подобные микросхемы имеют соответственно 4, 8,16 или 32 одинаковых матриц ячеек памяти. Таким образом, при поступлении на входы микросхемы адреса ячейки производится одновременное чтение (запись) всех ячеек, находящихся по данному адресу, но в различных матрицах (рис. 2). В этом случае одновременно считывается, записывается сразу несколько бит информации. Например, если микросхема имеет 8 линий ввода/вывода (соответственно 8 матриц), то CPU может считывать (записывать) информацию побайтно.

Количество линий ввода/вывода определяет разрядность шины ввода/вывода микросхемы.

Рис.2. Структурная схема микросхемы памяти 1x4 Мбит

Количество бит информации, которое хранится в ячейках каждой матрицы, называется глубиной адресного пространства {Depth Адрес, бит) микросхемы памяти.

Таким образом, общая емкость микросхемы памяти определяется произведением глубины адресного пространства на количество линий ввода/вывода (разрядов). Например, емкость микросхемы памяти, имеющей глубину адресного пространства 1 Мбит и 4 линии ввода/вывода (четырехразрядную шину ввода/вывода), составляет 1 Мбитх4 = 4 Мбит.

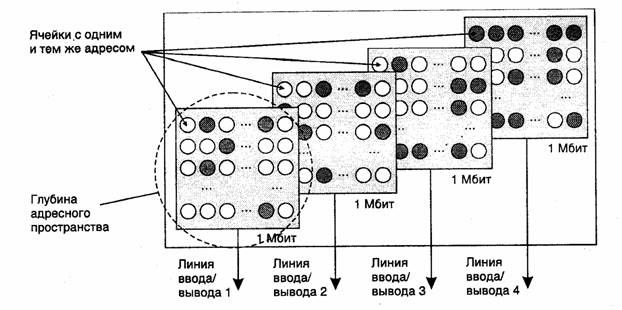

Для срабатывания синхронных элементов смены сигналов на входах недостаточно. Необходим дополнительный тактирующий сигнал, который подается на соответствующий вход. В качестве такого сигнала выбран тактовый сигнал системной шины. Этот сигнал задает частоту смены информации в определенные моменты времени. В эти же моменты обновляется информация на выходах элементов. Таким образом, процессы записи и считывания информации в память строго привязаны к тактам CPU или шины.

Этот метод синхронизации применяется в микросхемах SDRAM. Здесь тактовые сигналы синхронизированы с частотой процессора. Поэтому память и процессор работают синхронно без циклов ожидания.

За счет исключения циклов ожидания сократилось время выполнения команд и передачи данных. Современные микросхемы SDRAM могут работать на тактовых частотах от 100 до 266 МГц.

Рис.3

Рис.3

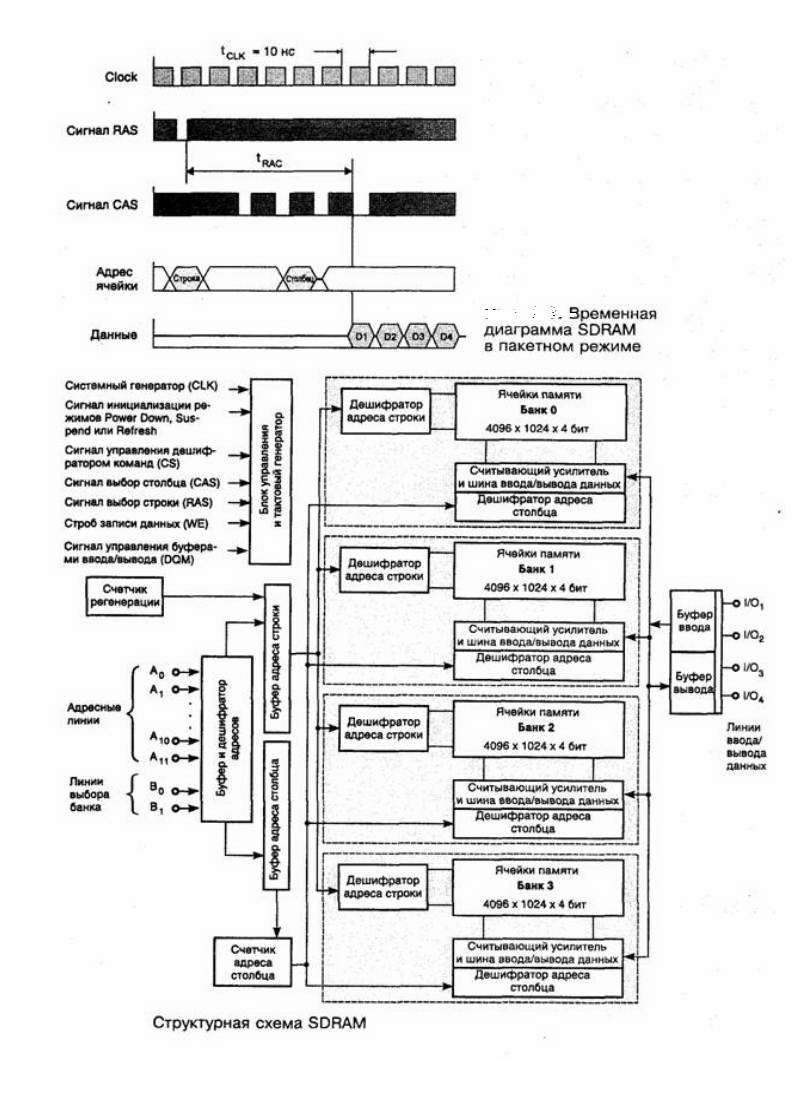

Внутренняя архитектура SDRAM предполагает два или более банка. Структурная схема SDRAM, имеющая 4 банка емкостью по 4 Мбит и 4 линии ввода/вывода, представлена на рис. 3.

Вам необходимо сделать описание работы этой схемы в качестве домашнего задания!!